Volume 19 Number 1 February 1995 ISSN 0350-5596

Informatica

**An International Journal of Computing and Informatics**

Special Issue: Parallel and Distributed Real-Time Systems Guest Editors: Marcin Paprzycki Janusz Zalewski

Profile: Haneef Fatmi

The Slovene Society Informatika, Ljubljana, Slovenia

# Informatica

# An International Journal of Computing and Informatics

Basic info about Informatica and back issues may be FTP'd from ftp.arnes.si in magazines/informatica ID: anonymous PASSWORD: <your mail address> FTP archive may be also accessed with WWW (worldwide web) clients with URL: ftp://ftp.arnes.si/magazines/informatica

Subscription Information: Informatica (ISSN 0350-5596) is published four times a year in Spring, Summer, Autumn, and Winter (4 issues per year) by the Slovene Society Informatika, Vožarski pot 12, 61000 Ljubljana, Slovenia.

The subscription rate for 1994 (Volume 18) is - DEM 50 (US\$ 34) for institutions, - DEM 25 (US\$ 17) for individuals, and - DEM 10 (US\$ 4) for students plus the mail charge DEM 10 (US\$ 4).

Claims for missing issues will be honored free of charge within six months after the publication date of the issue.

LATEX Tech. Support: Borut Žnidar, DALCOM d.o.o., Stegne 27, 61000 Ljubljana, Slovenia. Lectorship: Fergus F. Smith, AMIDAS d.o.o., Cankarjevo nabrežje 11, Ljubljana, Slovenia. Printed by Biro M, d.o.o., Žibertova 1, 61000 Ljubljana, Slovenia.

Orders for subscription may be placed by telephone or fax using any major credit card. Please call Mr. R. Murn, Department for Computer Science, Jožef Stefan Institute: Tel (+386) 61 1259 199, Fax (+386) 61 219 385, or use the bank account number 900-27620-5159/4 Ljubljanska banka d.d. Slovenia (LB 50101-678-51841 for domestic subscribers only).

According to the opinion of the Ministry for Informing (number 23/216-92 of March 27, 1992), the scientific journal Informatica is a product of informative matter (point 13 of the tariff number 3), for which the tax of traffic amounts to 5%.

Informatica is published in cooperation with the following societies (and contact persons): Robotics Society of Slovenia (Jadran Lenarčič) Slovene Society for Pattern Recognition (Franjo Pernuš) Slovenian Artificial Intelligence Society (Matjaž Gams) Slovenian Society of Mathematicians, Physicists and Astronomers (Bojan Mohar) Automatic Control Society of Slovenia (Borut Zupančič)

Slovenian Association of Technical and Natural Sciences (Janez Peklenik)

Referees: David Abramson (Australia), David Cliff (U.K.), Hugo de Garis (Japan), Terrence Forgarty (U.K.), David Green (Australia), Inman Harvey (U.K.), Li-Shan Kang (P.R. China), Raymond Lister (Australia), Zbigniew Michalewicz (U.S.A.), Stefano Nolfi (Italy), William Spears (U.S.A.), Jurij Tasič (Slovenia)

The issuing of the Informatica journal is financially supported by the Ministry for Science and Technology, Slovenska 50, 61000 Ljubljana, Slovenia.

# PROFILES

Profiles is a peculiar gallery of personalities in the field(s) covered by Informatica. To remember the readers, in this column we have had the profiles of the following researchers: Terry Winograd—AI and cognitive science philosopher and researcher (1/93); Jiří Šlechta—physicist and cyberneticist (2/93); Hubert L. Dreyfus—American philosopher of Being and critic of the traditional AI approach (3/94); Gheorghe Tecuci—machine learning and knowledge acquisition researcher (4/93); Robert Trappl—AI scientist and medical cyberneticist (1/94); Branko Souček—computer engineer and author of the six generation computing (2/94); and Hiroaki Kitano—inventor of computer simultaneous translation and AI researcher (3/94).

Professor Haneef Fatmi is a well-distinguished researcher, teacher, and organizer especially in the field where the most attractive development of scientific thought and technological development is expected, that is, in the field of cybernetic systems and machines. It is to stress that he is the chairman of a symposium held within the large cybernetics conference in the coming August, in Namur, Belgium.

# Haneef Fatmi

Haneef Fatmi is currently Honorary President of the Cybernetics Society of the United Kingdom. He is also a member of the Governing Body of the International Association for Cybernetics, Namur, Belgium and the Governing Body of the journal "Cybernetica". In addition he is a Senior Member of the American Institute of Electronic and Electrical Engineers. For his outstanding services for the advancement of Cybernetics and information theory he was presented a Deed of Appreciation by the Cybernetics Society in 1992, founding in perpetuity a "Fatmi Lecture in Cybernetics".

<sup>5</sup>Dr. Fatmi was educated at the Inns of Court School, Lincoln's Inn, London, where he obtained his Barrister's Degree, and Imperial College London where he was awarded a PhD degree for his work on plasma electrodynamics and information theory in 1961. From 1961 he worked on various problems of plasma electrodynamics and information theory in collaboration with Professor Dennis Gabor, FRS, Nobel laureate at Imperial College London, and the Atomic Energy Research Establishment Harwell, U.K. In 1968 he was appointed Director of the Cybernetics Research Group at the University of London and served in that capacity until recently. He has successfully directed over 30 PhD and 100 Master's projects in cybernetics.

In 1970 Haneef Fatmi published a world famous Definition of Intelligence in *Nature*, London which was a subject of comments by the leading researchers all over the world. It was republished by the Institute of Physics as one of the 2000 leading quotations of all times. The subject matter of the Definition was used by Professor H.B. Barlow to investigate a new approach to the measurement of intelligence and to relate guesswork, language and intelligence under the same common ground.

During the last 25 years Haneef Fatmi and his collaborators published over 150 technical papers on various aspects of cybernetics, informatics, artificial intelligence, robotics, knowledge-based systems, communications, control and information theory, all over the world.

His main research interests include the development of a novel approach to human psychology based on the understanding of psychophysiological mechanism of perception and awareness; development of a novel theory of cybernetics and intelligence machines; definition of intelligence in humans and the machines; intelligent neural networks and systems; distributed computing, control and communications networks; compression of data by pattern recognition and ruledbased algorithms; forecasting of financial data. Some of his papers has been published in *Informatica*.

#### Publications

Limited space does not allow to give a complete list of Dr. Fatmi's publications. Below is a short list of selected papers.

Gabor, D. and Fatmi, H.A., "A thermionic generator," Nature, London, 1961, 868.

Gabor, D. and Fatmi, H.A., "The theory of gas discharges with extraneous ion supply," Advanced Energy Conversion, IEE, London, 1964, 307.

Fatmi, H.A. and Young, R.W., "A definition of

Haneef Fatmi

intelligence," Nature, London, 1970, 97.

Fatmi, H.A., "The concept of a creative society," Electronics and power, IEE London, 1974.

Fatmi, H.A. and Resconi, G., "A new computing principle," Nuovo Cimento, Bologna, Italy, 1988, 239-242.

Fatmi, H.A. et al, "Theory of cybernetics and intelligent machine," in Proc. General Systems, USA, 1990, 123-164.

Lee C.C. and Fatmi, H.A., "Run-time support for parallel functional programming," J. of Systems and Software, Sept. 1991.

Fatmi, H.A. et al, "The nature of the stochastic method in cybernetics," in Proc. Int. Congress on Cybernetics, Belgium, 1972, 328-333.

Fatmi, H.A. et al, "Principles of discrimination in pattern recognition," Biokybernetik, Germany, 5, 1974, 281-287.

Fatmi, H.A. et al, "The concept of associative memories," in Proc. Int. Congress on Cybernetics, 1980, 303-310.

Fatmi, H.A. et al, "Parallel processors for cybernetic systems," Cybernetics and Systems, USA, 11, 1982, 179-192.

Fatmi, H.A. and Todd, S.J., "A cybernetic approach to intelligence based space system," in Proc. IEEE-SMC, New York, 1176-1181.

Ciupa, M. and Fatmi, H.A., "An expert system for data networks and services offering strategic planning support," in Proc. Network 90, UK, 241-250.

Oliver, A. and Fatmi, H.A., "Nonlinear adaptive filtering by the Gabor-Kolmogorov method," IEE Control, UK, 1991, 105-110.

Russel, I.E. and Fatmi, H.A., "A novel approach to interface design for a neural network expert system," IEEE IJCNN, USA, 1991, 384-388.

Sherif, H.T. and Fatmi, H.A., "3-dimentional moving object recognition by the neuro-optic field," IEEE IJCNN, China, 1992, 637-640.

Gilani, S. and Fatmi, H.A., "Organizational professional contextual issues," in Proc. Int. Congress on Cybernetics, 1992, 199.

Khan, H.U., Ahmad, J., Mahmood, A. and Fatmi, H.A., "Text compression as rule based pattern reorganization," IEE Electronics Letters, 29(20), 1993, 1752-1753.

Khan H.U. and Fatmi, H.A., "Text compression using rule base encoder," IEE Electronics Letters, 30(3), 1994, 199-200.

Mahmood, A., Khan, H.U. and Fatmi, H.A., "Adaptive file allocation in distributed information systems," Informatica, 18(1), 1994, 37-46.

Mahmood, A., Khan, H.U. and Fatmi, H.A., "Data reorganization in distributed information systems," Informatica, 18(3), 1994, 325-336.

Mahmood, A., Khan, H.U. and Fatmi, H.A., "Adaptive file allocation in distributed computer systems," IEE Distributed systems and engineering journal, December 1994.

Khan, H.U., Mahmood, A. and Fatmi, H.A., "A novel approach to text compression," Informatica, 18(4), 1994, 485–490.

Ahmad, J. and Fatmi, H.A., "Recognition of objects data in computer integrated manufacturing," in Proc. IEE Control'94, 1994, 805-808.

Ahmad, J. and Fatmi, H.A., "Signal recovery by feed forward neural networks," in Proc. ITA'94, UK, 1994, 79-83.

Ahmad, J. and Fatmi, H.A., "A novel method of speech recognition using feed forward neural network," in Proc. IEEE-SMC, USA, 1994, 21-25.

Russel, I. and Fatmi, H.A., "A novel definition of expert knowledge in expert systems," in Proc. IEEE-SMC, USA, 1994, 2208-2211.

Khan, H.U. and Fatmi, H.A., "Application of pattern recognition in text compression," in Proc. IEEE-SMC, USA, 1994, 1657-1659.

Ahmad, J. and Fatmi, H.A., "Quadric neural network for the prediction of financial time series data," IEE world congress on computational intelligence, USA, 1994, 3667-3670.

Edited by A.P. Železnikar

# PARALLEL AND DISTRIBUTED REAL-TIME SYSTEMS: INTRODUCTION TO THE SPECIAL ISSUE

Marcin Paprzycki Science and Mathematics University of Texas-Permian Basin Odessa, TX 79762-0001, USA paprzycki\_m@gusher.pb.utexas.edu and Janusz Zalewski Dept. of Computer Science Embry-Riddle Aeronautical University Daytona Beach, FL 32114-3900, USA zalewski@db.erau.edu

The purpose of this Introduction is to present the rationale behind selecting the structure of this Special Issue. It follows the general scheme of real-time systems' development: from requirements specification, to design, to implementation. A bibliography of books on parallel and distributed real-time systems for the last ten years is also included.

Real-Time Systems have two major characteristics: they always interact with the environment other than the human operator, and usually deal with timing constraints, mostly in a form of deadlines on the reaction to external stimuli. Because responsiveness and timeliness are so important in their behavior, real-time systems are almost exclusively concurrent, that is, consist of multiple program units, usually called tasks or processes, running simultaneously to perform required functions. Concurrent execution of tasks on a single processor may be in many respects inadequate for achieving the required level of performance or required level of reliability – the two primary system requirements. Therefore the tasks are often moved to different interconnected processors, making a real-time system parallel or distributed. Although it is sometimes hard to distinguish between parallel and distributed systems, especially in real-time computing, the principal distinction between the two is that of the communication speed versus processing speed. If the communication time between processing units is negligible with respect to the processing speed, then the system is called parallel; otherwise it is distributed.

Our approach to real-time systems, in general, is based on the system development view: from application requirements, to specification and design, to implementation issues considered on three different levels, that is, programming languages, operating systems, and hardware architectures. From the system development point of view, it does not make any difference whether a system is to be implemented on a single processor or on a parallel or distributed architecture; the development process must proceed in the same way. Therefore the sequence of articles in this special issue resembles the system development process and is structured in that way.

The first article, by McKay and Atkinson, discusses one of the most demanding applications for a real-time system: a part of the NASA's Mission project. Our interest in this paper is not that much in the solutions, which are described on a relatively general level, but in system requirements, which include reliability, safety and security. The major characteristic of an application described in this article is that as systems get more and more complicated, a unified approach to account for critical system properties, such as those listed above, combined with real-time properties is needed. Such systems are usually called high-assurance systems or high-integrity systems.

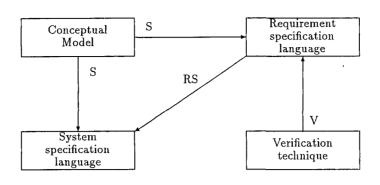

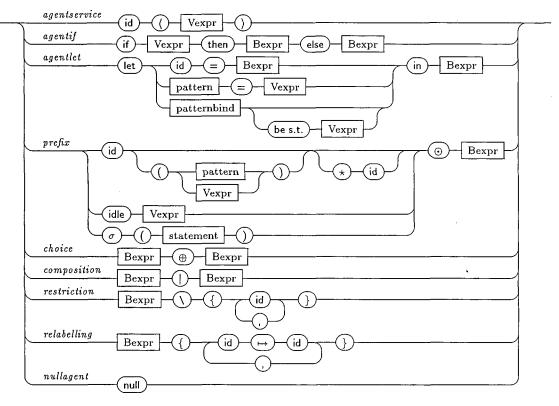

Because of extremely critical nature of highassurance systems, whose failure may involve loss of lives, loss of precious property or significant environmental damage, unconventional development methods are needed to ensure their correctness. One very promising, although not fully te-

M. Paprzycki, J. Zalewski

sted yet, approach to ensure correctness on the high level of development is the use of formal methods. These are the methods that employ proof techniques to ensure that the system is correct. In the article by van Katwijk and Toetenel, one such formal method, named MOSCA, is presented. MOSCA, based on an extension of VDM (Vienna Development Method), is a specification language providing facilities to specify real-time requirements for parallel and distributed applications.

Moving from the specification to the design level, system developers need to be equipped with modern methodology, usually consisting of the rigorous notation, techniques for development, and support tools. One such approach, objectoriented technology received significant attention in the last decade, but not necessarily for realtime systems development. In the article by Lin, Kung and Hsia, an object-oriented approach is presented to designing real-time systems whose critical system properties constitute a dominant part of the requirements and play a significant role in the development.

To convert the system/software design into a running application, the implementor usually faces a problem of dealing with programming language constructs to support design concepts. Of the many constructs that explicitly support real-time, parallel, and distributed programming, one still needs further development: exception handling. Colnarič, Verber and Halang deal with eception handling in their paper. Again, this problem is especially important because of the necessity to meet critical requirements in exceptional situations and the major contribution of this article is in providing exceptions on the language level.

If the implementation is to run according to the specification, the language constructs ought to be adequately mapped onto and supported by the operating system kernel. A real-time kernel, and especially a parallel or ditributed real-time kernel, needs to provide specific functionality which is very different from traditional understanding of an operating system. Corresponding problems are so critical that this special issue includes four articles related to this subject.

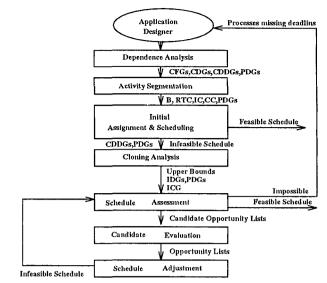

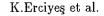

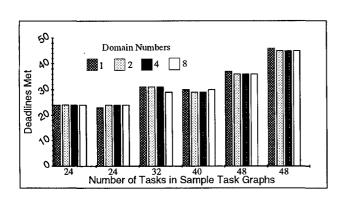

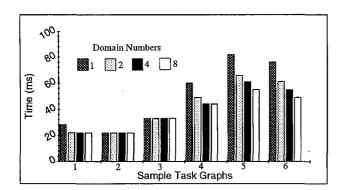

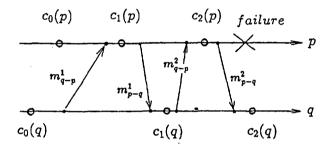

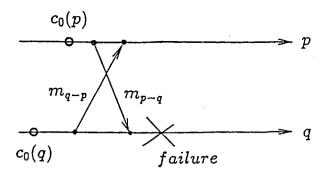

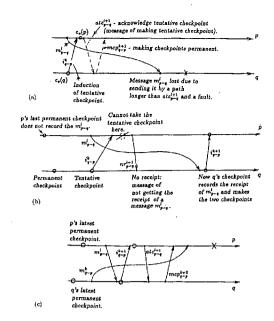

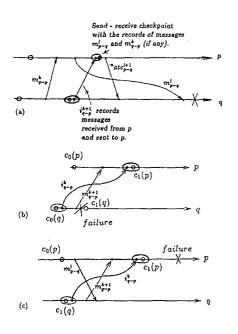

The first paper in this group, by Yu and Welch, presents an off-line scheduling approach based on the analysis of tasks' behavior for concurrency enhancement. The second paper, by Davari and Dhall, discusses two heuristic on-line algorithms to solve the allocation problem, that is, the assignment of tasks to processors so they can successfully meet deadlines. The next paper, by Erciyeş, Özkasap and Aktaş, describes a dynamic load balancing mechanism for massively parallel processing systems, and finally, a paper by Wòjcik and Wòjcik presents a universal method of achieving fault tolerance in a distributed system via checkpointing.

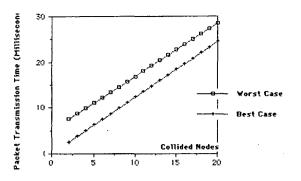

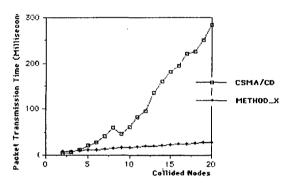

As the implementors well know, finding the perfect solutions to the most difficult software problems may be not enough, if the underlying hardware architecture is not functioning properly. From the multitude of problems which can be listed on the architecture level of a parallel or distributed real-time system, only one is tackled here, that of hardware guarantees on communication deadlines. Tchouaffe and Zalewski, in their article, deal with the problem of predictability of Ethernet – one of the most widely used local area networks.

Although we attempted to provide readers with a comprehensive coverage of problems and their solutions in parallel and distributed real-time systems, certainly no such coverage can be exhaustive. Those readers who are especially interested in this topic and want to pursue further studies may want to look into three other collections of papers [12, 18, 27] or access some of the books on this subject which have been published throughout the last ten years and are listed below.

## Acknowledgements

The following reviewers are gratefully thanked for their time and effort to make this special issue a reality:

- Azer Bestavros, Boston University, USA

- Travis Craig, University of Washington, USA

- Hesham El-Rewini, University of Nebraska-Omaha, USA

- Rod Howell, Kansas State University, USA

- Eric Johnson, New Mexico State University, USA

- Gilad Koren, Bar-Ilan University, Israel

- Phil Laplante, Fairleigh-Dickinson University, USA

- Bud Lawson, Lawson Publishing & Consulting, Sweden

- Joseph Y-T. Leung, University of Nebraska– Lincoln, USA

- Doug Locke, Loral Federal Systems, USA

- Daniel Mossé, University of Pittsburgh, USA

- Jerzy Nogieć, Fermilab, USA

- Warren Persons, Lawrence Livermore National Laboratory, USA

- Gary Preckshot, Lawrence Livermore National Laboratory, USA

- Michael Quinn, Oregon State University, USA

- Felix Redmill, Redmill Consultancy, UK

- Bo Sanden, George Mason University, USA

- Przemysław Stpiczyński, University of Maria Curie-Skłodowska, Poland

- Ken Tindell, University of York, UK

## References

- Atkinson C., T. Moreton, A. Natali (Eds.), Ada for Distributed Systems, Cambridge University Press, London, 1988

- [2] Bishop J. (Ed.), Distributed Ada: Developments and Experiences, Cambridge University Press, London, 1990

- [3] Conte G., D. Del Corso (Eds.), Multi-Microprocessor Systems for Real-Time Applications, Reidel Publishing, Dordrecht, 1985

- [4] de la Puente J.A., M.G. Rodd (Eds.), Distributed Computer Control Systems 1994, Pergamon Press, Oxford, 1994

- [5] Fleming P.J. (Ed.), Parallel Processing in Control: The Transputer and Other Architectures, Peter Peregrinus, Stevenage, UK, 1988

- [6] Fortier P.J., Design and Analysis of Distributed Real-Time Systems, McGraw-Hill, New York, 1985

- [7] Garcia Nocetti F., P.J. Fleming, Parallel Processing in Digital Control, Springer-Verlag, London, 1992

- [8] Irwin G.W., P.J. Fleming (Eds.), Transputers in Real-Time Control, John Wiley and Sons, New York, 1992

- [9] Knuth E., M.G. Rodd (Eds.), Distributed Databases in Real-Time Control, Pergamon Press, Oxford, 1989

- [10] Kopetz H., M.G. Rodd (Eds.), Distributed Computer Control Systems 1991, Pergamon Press, Oxford, 1992

- [11] Lawson H.W., Parallel Processing in Real-Time Applications, Prentice Hall, Englewood Cliffs, NJ, 1992

- [12] Lawson H.W. (Ed.), Special Issue on Parallel Processing in Embedded Real-Time Systems, Microprocessing and Microprogramming, Vol. 40, No. 2-3, April 1994

- [13] Liebowitz B.H., J.H. Carson, Multiple Processor Systems for Real-Time Applications, Prentice Hall, Englewood Cliffs, NJ, 1985

- [14] Lukas M.D., Distributed Control Systems: Their Evaluation and Design, Van Nostrand Reinhold, New York, 1986

- [15] Motus L., S. Narita (Eds.), Distributed Computer Control Systems 1989, Pergamon Press, Oxford, 1990

- [16] Nielsen K., Ada in Distributed Real-Time Systems, McGraw-Hill, New York, 1990

- [17] Popovic D., V.P. Bhatkar, Distributed Computer Control for Industrial Automation, Marcel Dekker, New York, 1990

M. Paprzycki, J. Zalewski

- [18] Reeves D.S., K.G. Shin (Eds.), Special Issue on Parallel and Distributed Real-Time Computing, IEEE Parallel and Distributed Technology, Vol. 2, No. 4, Winter 1994

- [19] Rodd M.G., Th. Lalive d'Epinay (Eds.), Distributed Computer Control Systems 1988, Pergamon Press, Oxford, 1989

- [20] Rodd M.G., K.D. Mueller (Eds.), Distributed Computer Control Systems 1987, Pergamon Press, Oxford, 1988

- [21] Rogers E., Y. Li (Eds.), Parallel Processing in a Control Systems Environment, Prentice Hall, Englewood Cliffs, NJ, 1993

- [22] Schuetz W., The Testability of Distributed Real-Time Systems, Kluwer Academic Publishers, Boston, MA, 1994

- [23] Stein R.M., Real-Time Multicomputer Software Systems, Ellis Horwood, New York, 1992

- [24] Suski G.J. (Ed.), Distributed Computer Control Systems 1985, Pergamon Press, Oxford, 1986

- [25] Theus J., The Futurebus+ Handbook, VITA, Scottsdale, AZ, 1993

- [26] Thoeni U., Programming Real-Time Multicomputers for Signal Processing, Prentice Hall, New York, 1994

- [27] Welch L., D.K. Hammer (Program Chairs), Proc. 2nd IEEE Workshop on Parallel and Distributed Real-Time Systems, Cancun, Mexico, 28-29 April 1994, IEEE Computer Society Press, Los Alamitos, CA, 1994

- [28] Zalewski J. (Ed.), Advanced Multimicroprocessor Bus Architectures, IEEE Computer Society Press, Los Alamitos, CA, 1995

# Supporting the Evolution of Distributed, Non-stop, Mission and Safety Critical Systems

Charles W. McKay and Colin Atkinson University of Houston - Clear Lake 2700 Bay Area Boulevard, Houston, TX. 77058. Phone: +713 283 3830, Fax: +713 283 3869 E-mail: mckay@cl.uh.edu

Keywords: distribution, environments, non-stop, real-time, safety-critical

Edited by: Marcin Paprzycki and Janusz Zalewski Received: February 12, 1994 Revised: October 20, 1994

Accepted: January 9, 1995

In coming years embedded systems which are distributed, non-stop and "mission and safety critical" (MASC) are likely to assume increasing importance. The construction, operation and maintenance of this class of system presents a unique blend of problems which many traditional tools and techniques, targeted to just one problem area, cannot currently address. This paper provides an overview of a promising, model-based framework for supporting such systems that has been developed as part of NASA's MISSION project. Based on well-established research advances in computing, the MIS-SION approach provides a domain-specific, life-cycle support framework encompassing three separate environments: host, integration and target. Although the individual elements of the framework are not all new, their synergistic packaging within the MISSION project is believed to be unique. This paper focuses upon the systems-level support for applications executing in the target environment.

# 1 Introduction

An embedded system is a computer system which is constructed to monitor and/or control a set of devices and processes constituting some larger engineering system. The term "embedded" is used to reflect the fact that such computing systems are physically encapsulated by the engineering system they monitor/control. An important characteristic of embedded systems is that they are typically real-time - not only must they produce the correct result, but they must do so within a specified period of time. Because of their monitoring and controlling role, the reliable execution of an embedded system is often critical to the success of the overall mission and to the safety of life, health, property or the environment. In such circumstances the embedded system is termed a mission and safety critical (MASC) system.

As the reliability and efficiency of networking technology has increased, and the cost of microprocessors has plummeted, there has been an increasing trend towards the implementation of embedded systems as distributed systems made up of autonomous, cooperative processors interconnected by communication channels. Not only does such an implementation enable processing power to be located physically close to the individual devices in the system, but it also opens up the possibility of extending, or modifying, parts of a system while other parts are still running. In other words, it opens up the possibility of building non-stop systems which can be dynamically upgraded and reconfigured.

In coming years there is likely to be an increasing need for embedded systems which exhibit all the properties identified above, namely the properties of being mission and safety critical, realtime, distributed and non-stop. Such systems are essential in extremely hostile and/or inaccessible environments, such as space or the depths of the ocean, and are therefore crucial to pending NASA projects (e.g., space station, lunar outpost, human missions to Mars). Such systems are also likely to be used in large process control applications such as factory automation, power plant control, etc.

In recent years numerous projects have addressed one or more of the issues mentioned above. To meet the real-time requirements of embedded systems, for example, advanced scheduling techniques have been developed (e.g., rate monotonic scheduling [37] and best effort decision making [20]). The requirements of distribution, on the other hand, are addressed by new and more powerful networking hardware and communications protocols such as the Open Systems Interconnection Model [33]. Reliability and safety are addressed by advanced software features such as distributed nested transactions [24], while the needs of non-stop operation and dynamic upgradeability [44, 42] are addressed by modular approaches to operating system organization.

Because of the complex way in which the above characteristics are interrelated in embedded systems, however, it is not always possible to use these tools and techniques together in a system which exhibits several, if not all, of these properties. Often a technique which is very successful at solving one particular problem cannot be used with another technique developed to solve another problem because of the way they overlap and interact. The different techniques, and in particular the combination of technologies, have the potential to introduce new problems or exacerbate others. This difficulty is compounded by the fact that systems of this kind are inherently complex and typically very large. In fact, some of the largest software systems to date fit into this category.

For this reason, rather than tackling individual aspects of the problem of supporting the evolution of non-stop, distributed, real-time, MASC systems, the MISSION<sup>1</sup> project has focused on defining the overall development strategy and infrastructure into which such solutions will fit. Specifically, this work has two main thrusts. The first part is to lay the foundation for a new generation of integrated systems software for the target environment in which MASC computing applications are deployed and operated. The second part is to define an accompanying infrastructure which is capable of supporting the construction, verification, reuse and maintenance of the kind of software artifacts required in the target environment. The MISSION approach is believed to be unique in the integration of these advancements across the three environments.

This paper provides an overview of the MIS-SION approach for supporting distributed, nonstop MASC systems with a particular focus upon the systems software support for applications executing in the target environment. Before describing the approach itself, however, we first describe the main issues that arise in the construction and maintenance of this type of system. In addition to providing a definition and description of each issue, we identify some of the applicable terminology and technologies. The following section then describes the MISSION strategy for dealing with these issues, first introducing the general context in which MASC software is developed, operated and maintained, and then describing the target architecture. We conclude by describing each of the subsystems making up this architecture.

## 2 Principal Issues

Important issues and requirements for MASC computing systems operating in hostile environments have been discussed in publications such as [1, 14, 36, 38]. This section discusses only five of the principal issues: life cycle approaches; distribution; safety; reliability, security and integrity; and fault tolerance.

Clearly, the requirements for the project as a whole are driven by the target environment. The life cycle requirements for the integration environment, which serves as the site from which the target is monitored, controlled and updated, are principally driven by the need to provide safe and affordable support for the target environment over its complete lifetime. The requirements for both the target and integration environments are, in turn, the principal drivers of the life cycle requirements of the host environment, which is the place where the initial application development and testing takes place. Since the entire set of life cycle requirements for this class of MASC computing applications and systems will probably never be known in advance, an iterative approach to life cycle support is essential.

<sup>&</sup>lt;sup>1</sup>MISsion and Safety crItical SuppOrt ENvironment

#### 2.1 Life Cycle Approaches

As might be expected, one of the major deficiencies in the current state of the practice for this domain is the lack of predictably-dependable, integrated approaches [11, 23, 29]. Such approaches should be traceable, controllable, and applied iteratively from the system's initial inception through to its retirement. MISSION's goal of defining and verifying such approaches is mirrored in other projects such as Spring [11] and the PDCS project [29].

An important goal of MISSION is to demonstrate that an object-oriented discipline can be used to control the complexity of this MASC target environment. Related issues include the application of the object-oriented discipline to the design of the generic architecture for the target environment systems software. Of particular importance is the evolution of a MASC kernel for this systems software [26, 39, 29]. The kernel is intended to provide a small but powerful set of mechanisms designed especially to support tractable, rigorous reasoning about MASC functions and systems. Support for such reasoning is critical for the infrastructure in the integration and host environments. In addition, safe and affordable approaches should consider the integrated issues of the software, (both applications level and systems level), the hardware, communication links and human-machine subsystems as well as interactions with the environment in which the system is deployed and operated. Techniques currently addressing these system level issues are not well integrated. The Alpha project [26] shares the goal of using the object paradigm to develop systems software that supports tractable, rigorous reasoning about MASC properties.

## 2.2 Distribution

Providing support for distributed operations is both a problem and an opportunity. Distribution should facilitate new and more powerful forms of fault tolerance along with opportunities to improve performance for real- time command and control systems [30, 41]. Related issues include when and how to assign software components to physical processing sites [5] and what support can and should be provided for migrating components among processing sites [45]. This support must be integrated with the ability to dynamically evolve and reconfigure both the applications and the systems software in the non-stop, distributed target environment (DTE). Unfortunately, no known system currently integrates a full set of acceptable solutions to these requirements with the needed attention to safety.

The need to capture a broad spectrum of information for system objects is even more crucial when real-time decisions are to be made [40]. In a distributed system the universal system state changes faster than can be communicated throughout the system [15]. Furthermore it may never be possible to "snap-shot" a view of the entire system state at any point in time. Decisions therefore must often be made in environments of incomplete and sometimes inaccurate data [20]. The goal of safely supporting dynamic evolution and reconfiguration of non-stop, distributed systems is shared by the Real Time Mach project [43].

#### 2.3 Safety

The following working definition of safety is used in this project "safety is the probability that a system, including all hardware, software, communication links, human-machine subsystems, and interactions with the environment, will provide appropriate protection against the effects of faults, errors, and failures which could endanger life, health, property, or the environment." Safety depends upon related issues such as integrity, reliability, security and others to be discussed in the following subsections. Safety cannot be guaranteed, especially not for the class of MASC computing applications under discussion in this paper. Many important risks, nevertheless, can be managed to improve the probability of sustaining safety across the life cycle [28, 7]. MISSION supports the traditional goal for aerospace applications that no single point of failure can endanger a mission and no two points of failure can endanger safety.

Safety is the most important aspect of any distributed MASC computing system. The system must guard itself against any event or action, intentional or accidental, that compromises its safety [6]. Safety requirements should be considered at each point of the system's life cycle [19, 34].

The ultimate aim of the work reported in this

paper is to define a small but powerful set of constructs that can be used to compose MASC computing applications and systems. These constructs are being defined to support safety properties. Systems composed of such constructs should facilitate tractable, rigorous reasoning about safety. The MISSION project is fairly unique in its emphasis on evolving and verifying approaches to composing safe, non-stop, real time, distributed systems.

#### 2.4 Reliability, Security and Integrity

The safe and affordable support of lives, health, property, environment, and mission in the target environment depend upon system level reliability, security and integrity. System reliability refers to the ability of the system to function under stated conditions for a stated period of time [25], and should be maximized for MASC applications and systems. This requires more than certification of correct software components and highly reliable hardware components. It also requires systems level design for fault tolerance and survivability [16, 31].

System security refers to the protection of the system from accidental or malicious access, use, modification, destruction, or disclosure [9]. Distributed systems which support a diverse group of users are particularly vulnerable to problems which result from improper access to information and other resources. At the minimum, protection is necessary for inadvertent access due to program or operation error. At the other extreme, deliberate disruption must be prevented. The MISSION project seeks to provide security to at least the multilevel security class B3 of the DoD standard for security [9]. Such security should be supported within the target environment and in all its interactions with the integration environment.

System integrity refers to the ability of the system to perform its intended function irrespective of changes in its operational environment [32, 8, 31]. The MISSION approach for ensuring integrity in the target environment builds upon research in executable assertions[35]; monitors [18]; checkpointing and recovery schemes [21]; and distributed, nested transactions [24]. The approach also introduces the concept of the integration environment. These aspects of the approach are discussed in more detail in the following section.

#### 2.5 Fault Tolerance and Recovery

In a perfect world, functionally correct software, hardware, communication links, and human machine subsystems would operate safely and reliably in their intended environment. Unfortunately, in the domain addressed by MISSION, faults, errors, and failures will occur which could be disastrous if not detected and handled properly. MASC systems are needed which can tolerate such problems or, when the problems cannot be tolerated, enact survivability policies.

A failure means that a functional unit can no longer satisfy its requirements at run-time, and may be caused by a defect in the software design or implementation. A fault occurs at run-time and may leave errors in some part of the system, and may sometimes lead to failures. Detection may refer to the detection of either a fault, an error or failure [27]. Recovery refers to the process of restoring normal operation after the occurrence of a fault or failure [21].

Classes of faults, errors, failures, and their combinations should be identified and prioritized according to their probability of occurrence during execution, and the consequences of not properly dealing with them [7, 12]. A safe system is not only able to monitor its status and detect an occurrence of such classes as soon as possible, but can also analyze and control the propagation of the effects and recover safely.

The fundamental issue behind MASC software support is handling the consequences of faults. Two approaches are commonly identified: fault tolerance and fault avoidance. Fault avoidance depends on ultra-reliable hardware, early detection of low-level faults with redundant processing, and the ability to use this redundancy to mask faults in the system from its environment. Specifically, the faults are masked from the system state vectors. Avoidance techniques are valuable but not sufficient [13, 41].

Large, complex systems with intricate dynamic interactions severely limit the ability of fault avoidance to assure safe and correct performance. Even if systems with millions of lines of defect-free code could be built (and they currently can not), they would not execute without faults, errors and failures throughout a long, non-stop, operational lifetime. Some combination of hardware failure, communication links failure, operator errors, latent software defects or acts of providence will cause problems at runtime. Many of these can be tolerated if the software is built to do so. Others cannot be tolerated but survivability can be maximized if the software is so designed [26].

Fault tolerance is a complementary approach to fault avoidance. Fault tolerance is based upon the assumption that any computation might become defective and result in an erroneous system state vector. Either forward or backward recovery schemes may be used to restore the system to a safe and correct state. Since the possibility for the introduction of such problems exists at all levels of the software hierarchy, it should be considered and addressed at all levels. In so doing, the ability to manage or at least mitigate the effects of faults, errors and failures throughout large and complex systems may be made possible [4, 12, 13, 16, 17, 41]. The MISSION goal to leverage combinations of fault avoidance and fault tolerance in support of MASC requirements is similar to a goal of the MARS project [17].

## 3 The MISSION Approach

The previous section has described some of the principal issues involved in the construction and maintenance of distributed, non-stop MASC systems. In this section we provide an overview of the MISSION approach for tackling the issues, and integrating the various separate technologies that have been developed to date. In particular, we describe how the MISSION approach addresses the need for precise (semantic) modeling, three computing environments, and a generic architecture for the systems software that executes MASC applications.

#### 3.1 Semantic Modeling

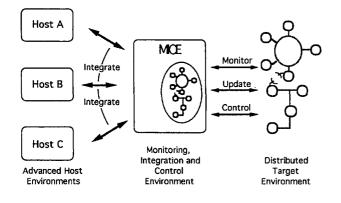

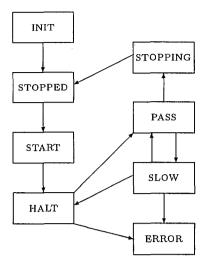

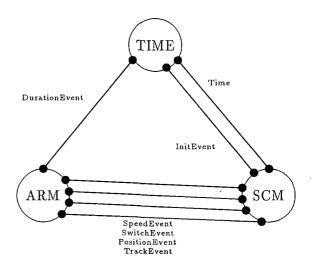

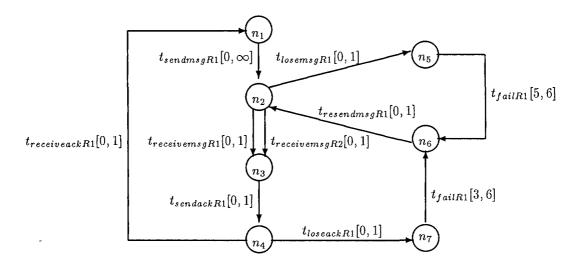

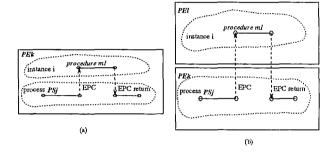

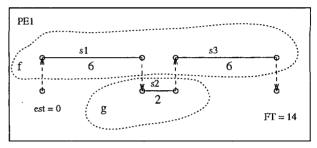

As depicted in Figure 1, the key requirements originate within the distributed target environment (DTE), flow traceably and cumulatively across the integration environment to the host environment and back. System level modeling is fundamental to improved understanding and progress toward safe solutions. The need for such modeling extends beyond the final executing system, and encompasses also the interrelated processes that produce the improved solutions. Such modeling of products and processes has implications for all three environments in the MISSION approach.

A key requirement for an integrated solution is the capability to model system level components and interrelationships among software, hardware, communication links, human-machine subsystems, and their operational environment. The representation of such system level components and their interrelationships should facilitate automated support for tractable, rigorous reasoning about their MASC properties.

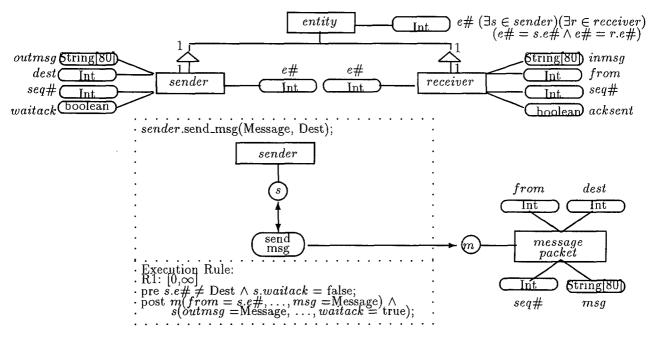

To respond to these needs, the MISSION team has adapted an object-oriented modeling approach developed by Embley, Kurtz and Woodfield [10] and augmented the approach with additional semantics in entity- attribute/relationshipattribute (EA/RA) form. The approach by Embley et. al. is based upon a formal definition and depicts object-oriented models in three views. Object-relationship models provide the structural view of the part of the system being modeled. The behavior of each object class that appears in the object-relationship models is depicted in an object-behavior model. Interactions among object classes are depicted in objectinteraction models. Although the combination of the three modeling views does support a large degree of tractable, rigorous reasoning about the systems being modeled, the semantics defined in the approach do not provide sufficient granularity to capture all details of interest in the MISSION project. Examples include redundant objects, bindings between software and hardware, workload profiles, reconfiguration of systems resources, etc. An entity- attribute/relationship-attribute (EA/RA) form of representation which has been systematically extended to include object classes, relationship sets, states, transitions, interactions and attributes is a feasible choice for representing these system level components, interrelationships, and their MASC properties. The IRDS standard [3] for this form of semantic representation has been legally extended by the MISSION team to meet these needs. However, a discipline is required to systematically address the inherent complexity within the problem space. The same discipline should also control the associated com-

Figure 1: Three Environments

plexity of the processes of evolving and sustaining safe and affordable solutions.

As a scenario to illustrate the modeling discipline and processes advocated by MISSION, consider a proposal to replace and to add types and instances of vehicles in NASA's Space Transportation System. The MISSION process would begin with domain analysis to determine the number of product lines needed (types of vehicles in this example) and the variations needed among instances of each type. Along with attributes such as costs, benefits, risks, opportunities, etc., this "business model" would be captured in objectoriented form and conveyed to the client. Based upon priorities, constraints, and other business and political factors shaping decisions and commitments, the business model would be mapped to a scoping model to identify which product lines and their variations will be evolved, when, and in what order. The object-oriented scoping model would then be mapped to a "concept of operations" model for each product line and its variations. System requirements modeling for the domain would then proceed by revising the concept models to represent common requirements and constraints as-well-as differences among the product lines and their variations. Later, this "domain model" would be mapped to a partitioning and allocation of requirements and constraints among models of: software, hardware and communications, and human interfaces. This stage would be followed by the creation, evaluation and selection of generic architectures appropriate for the domain. The domain engineering process would continue and would eventually be followed by application engineering to create specific instances of the product lines.

Some important points to be noted about this scenario are as follows. First, all products of the process are represented in an extended object- oriented form (i.e., extended via EA/RA notations) whether the products are business models, models of system requirements and constraints, or models of software, hardware and communications, human interfaces, and interactions with the environment. Second, a complete set of semantic information typically requires three views of the object models. Third, tools exist to facilitate such modeling and reasoning about the models. Fourth, the domain engineering processes and the application engineering processes that evolve these products are also represented as object models.

Precise semantic modeling using an objectoriented discipline provides the foundation for constructing system level fault tolerance and avoidance. Systems built from such models can also be designed and verified to enforce policies for survivability when faults and failures occur that cannot be tolerated or avoided. For example, to support fault tolerance, classes of faults, errors, and failures can be identified and modeled for the software, hardware, communication links, human-machine subsystems and operational environment that comprise the intended MASC computing system. Assertions can be formulated to provide context sensitive detection and responses for certain classes of faults, errors, or failures namely, those classes that are not only likely to occur but which will also produce unacceptable behavior and effects if they not properly handled. One or more monitors to enforce these assertion checks and responses can then be generated to accompany the functional software to the target environment.

Of the research projects that focus on domains overlapping with that of MISSION, MISSION is somewhat unique in its emphasis on process and methodologies that leverage object modeling as a unifying paradigm at the systems level. Alpha shares the commitment to software objects and Spring shares the commitment to tools and methods for the host and the target environment.

### 3.2 Three Environments

Developers of software for embedded systems have traditionally been concerned with two environments: the host environment (the computers on which all software requirements analysis, design, implementation, and testing is performed) and the target environment (the embedded computers on which the software is intended to execute). However, these two types of environments are insufficient for MASC systems which are developed by several different organizations, and which are required to execute non-stop. Typically there will be many "host" environments, each used to develop a part of the final system. For example, different host environments could be responsible for different (sub)applications to be added to the existing system. To enable the products from the various "hosts" to be combined, and to provide an interface to the software executing on the target environment, MISSION envisions a third environment - the monitoring, integration and control environment (MICE). The provision of a coherent framework for modeling the structure and behavior of MASC systems impacts all three environments throughout the full life-cycle of the system.

The Monitoring, Integration and Control Environment (MICE), is intended to mitigate the risk in evolving and sustaining remotely distributed, non- stop, MASC computing applications and systems. The MICE serves as an interface between the various hosts and the target environment and is the environment where software from the hosts is integrated. The MICE additionally serves to safely upgrade software components in the target environment, monitor the performance of the target environment, and possibly assist the target environment in performing major reconfigurations in response to faults. To properly perform these tasks the MICE must have up-to-date models of the structure, functionality, behavior and constraints of the elements of the executing target environment. The MICE must also present an appropriate command interface, and provide powerful diagnostic support.

The MISSION project is believed to be unique in its attention to the integration environment within a research context, although environments of this type have historically been an important part of NASA applications (e.g., the Mission Control Center for shuttle operations).

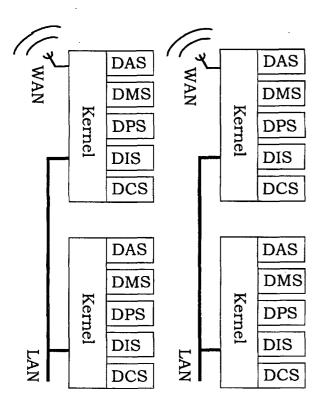

#### 3.3 Generic Architecture

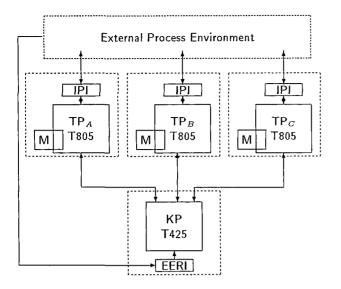

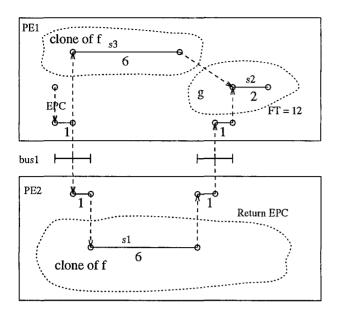

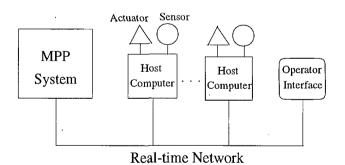

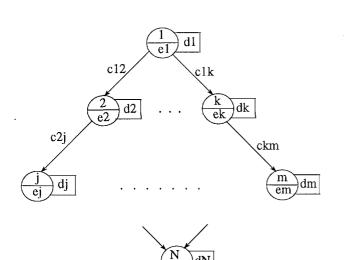

A generic solution architecture is proposed for the domain of MASC computing applications and systems addressed by the MISSION research. As shown in Figure 2, the target environment is a distributed system composed of interacting, multiprocessor clusters. Local area networks (LANs) may be configured from these clusters, and wide area networks (WANs) may be configured from these local area networks. The applications software on each cluster is supported by systems software providing intra- and inter-cluster communication and reliable execution in the presence of component failures. To limit the damage caused by faults, and to increase the feasibility of developing and sustaining such a system, the software on the processor clusters is separated into the following "firewalled" partitions<sup>2</sup> -

- 1. MASC Kernel

- 2. Distributed Application System (DAS)

- 3. Distributed Monitoring system (DMS)

- 4. Distributed Policy Systems (DPS)

- 5. Distributed Information System (DIS)

- 6. Distributed Communication System (DCS)

If, for example, a new space vehicle were required, the number and type of applications and the profile of the intended workload can be used to determine how many clusters (and with what resources), and what LAN and WAN resources will be needed.

Much of the research and development of distributed systems has evolved from an assumption of single processor nodes interconnected by LANs and WANs. Even multiple processor nodes have frequently been configured as "N redundant" processors to avoid certain types of faults. In effect, such processors process a single instruction and data stream with a "voting mechanism" to assure majority rule (e.g., the primary flight control system of NASA's space shuttles).

As a partial result of the "single processor node" mind set, attempts to evolve distributed

$<sup>^{2}</sup>$ By firewalled, we mean that certain steps have been taken to ensure that a fault, failure or error in one partition does not adversely affect other partitions.

Figure 2: Generic Architecture

systems with tightly constrained, real-time control functions have not been widely successful. Such systems typically experience severe performance problems in meeting their functional requirements. Attempts to integrate a software based approach to supporting systems level fault tolerance tend to exacerbate the overhead problem responsible for the poor performance.

Much of the performance overhead in a single processor node is associated with the time required for context switches. Unfortunately, the elimination of context switches can result in the loss of opportunities to help prevent faults that occur in the execution of one instruction stream from corrupting the subsequent execution of other instruction streams. A key concept of the MISSION approach is to "flatten" the traditional software architecture to take advantage of multiprocessing clusters as illustrated by the cluster architecture in Figure 2. If, for example, such a cluster was located at a geographical site with requirements for four local, hard constrained, real- time control functions, then as many as four or more processors could be assigned to the parallel processing of these control functions. Even if interaction existed among the four functions, parallel processing may offer benefits over a single processor. In the MISSION architecture, the units of functional code are intended to execute in parallel with coroutines on other processors that check for faults, errors, or failures. As long as no flaws are detected, only a minimal performance overhead is added to the execution of the functional code of the applications. Still another performance benefit may be derived by also allowing parallel execution of services and resources that are shared among the applications. For example, persistent information and communications may be organized in such as way as to maximize parallel processing among these subsystems and the applications as indicated in Figure 2.

The MISSION goal to exploit parallel processing capabilities among LANs and WANs of multiprocessing clusters is also a goal of other projects such as Alpha, Spring and Real-Time Mach. The approach to "flattening" the architecture to achieve the intended throughput improvements is particularly evident in Alpha and MISSION.

#### 3.3.1 The Clusters

MISSION clusters have the following properties. Clusters:

- do not share physical memory,

- have access to a hierarchy of memory subsystems including stable storage controlled by transaction mechanisms,

- may be connected to any number of LANs and WANs,

- may have predetermined types of hardware resources, including processors, added to a cluster without changing systems software,

- may fail completely or partially,

- may be repaired and returned to full service, typically without stopping processing,

- may be added/removed at any time,

- may have changes to applications and systems software made without stopping processing, and

- may control access to both physical and virtual systems resources.

C.W. McKay et al.

#### 3.3.2 The Communications Links

MISSION communications links must be able to tolerate faults, errors and failures which include messages which have lost parts, garbled parts, out-of- order parts, duplicated parts, or parts which are arbitrarily delayed.

#### 3.3.3 MISSION Computing Systems

MISSION computing systems are expected to tolerate, to a specified level, combinations of faults, errors and failures to include: communications failures, abortion of application and system program components, crashes of one or more clusters participating in an application, and lock cycles.

#### 3.4 The Kernel

The MASC kernel is a critical part of the MIS-SION approach to improving runtime support for the execution and evolution of MASC functions and components in the distributed target environment (DTE). It is similar to the "microkernels" of other projects such as Alpha, Mars and Spring, and provides the foundation on which the firewalled subsystems are built. These mechanisms directly affect the ability of the infrastructure in the integration and host environments to support the DTE. This is because the integrated approaches to semantic modeling are based upon the generic architecture of the DTE systems software.

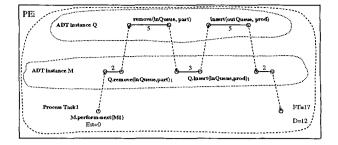

The kernel is responsible for encapsulating hardware and providing mechanisms to support the policies, operations, and interactions of the other five firewalled partitions. Any communication entering or leaving a partition is a result of invoking the kernel for a message passing service. No direct communication among partitions is allowed apart from with the kernel. The five firewalled partitions, shown in Figure 2, (DAS, DIS, DCS, DPS and DMS) are also referred to as the five firewalled subsystems. Thus, for example a DAS component that wishes to request a resource from the local DIS or from a remote DAS component must invoke a message passing service from the kernel. This modularity allows rigorous reasoning about the kernel independent of the sources or destinations of messages. Since the properties of the structure, functionality, behavior and constraints of the kernel can be assured, the same approach to rigorous reasoning can be independently extended to each of the five firewalled subsystems.

As in [2], MISSION treats the kernel's messagepassing relationships with the other subsystems as explicit, first class semantic entities. Protocols are used to describe allowable interactions, their constraints, and their responses to constraint violations, much as in the Mars project. In contrast with the Mars approach, however, MISSION does not assume a clock that is universally available to all clusters in real time.

## 3.4.1 Twelve Features of the Generic Architecture

The MISSION system architecture embodies twelve features which are either not found at all in today's systems software or are not found as an integrated set. There are at least two important reasons why this set of features is used. First, they facilitate the provision of runtime support needed for the domain of MASC computing applications and systems 'addressed by the project. Second, they facilitate precise modeling and the associated discipline of rigorous reasoning about the system. These twelve features are identified below:

- F1. Model-based reasoning

- F2. Firewalled partitions of applications and subsystems

- F3. Tailorable interfaces based on classes, objects and messages

- F4. Life cycle unique identification of classes, objects and messages at runtime

- F5. Extensible and modifiable sets of classes, objects and messages at runtime

- F6. Separation of policies and mechanisms

- F7. Multiple and adjustable levels of security and integrity

- F8. Synchronous and asynchronous communications mechanisms

- F9. Adaptable policies for scheduling, redundancy management and the management of other runtime services and resources

- F10. Stable storage for checkpointing and recovery

- F11. Distributed, nested transactions

- F12. "System" level fault tolerance and survivability through systems software.

We elaborate upon these features below.

### F1. Model-Based Reasoning

MISSION engineering processes and products emphasize semantically rich, object-oriented models to support tractable, rigorous reasoning about MASC properties. These models can be partially leveraged in the target environment since the kernel contains a finite set of mechanisms designed especially to support the interpretation, maintenance and modification of runtime models. For example, runtime policies are maintained in the DPS as models. In addition, current configuration details are also maintained as on-line models. When an overload condition arises at a cluster, interpretation of the overload policy in terms of the current configuration will determine the response (e.g., load sharing with another cluster or local load shedding).

Although model based reasoning is certainly not new, MISSION is believed to be one of the first projects to investigate its application to nonstop, distributed, MASC systems. Initial studies have focused upon its use in configuration management For example, a resource might initiate one particular recovery response under one set of conditions, and a different recover response under different conditions. Since most elements of the workload and system configuration are welldefined in the DTE models, context sensitive contingency determinations can often be made in parallel with workload processing and be available for rapid response in the presence of one or more anomalies of a predetermined type.

## F2. Firewalled Partitions

Firewalled partitions are used in MISSION to maximize the opportunities for identification, isolation, and selection of recovery capabilities. In the host environment, objects are created and assigned to one-and-only-one of the five firewalled subsystems or to the kernel. As the semantic models of the DTE applications and system are evolved, these objects are further allocated to specific clusters. This partitioning and allocation information is exported to the DTE for use by the kernel and the five subsystems. This means that if, for example, an application object executing in a cluster's DAS requests information from an object in the local DIS, the message is passed from the first subsystem to the second by invoking the kernel. Similarly, if an object in the cluster's DAS requests information from a DAS object in a remote cluster, the kernel recognizes that a local object is requesting information from a remote object and invokes the appropriate operation. The message is passed to the local DCS where a communication object will prepare to effect the remote communication.

The result of this organization is to isolate each partition of objects by explicit message passing through the kernel services. For example, suppose a DAS object passes a message to a DIS object which accepts the message and then fails. The opportunities for tolerating the failure are enhanced since the DAS object was preserved in a healthy state when the message was sent. In much the same way, different applications within the DAS, different information systems within the DIS, etc. are also protected from corruption within their own subsystems.

# F3. Tailorable and Extensible Interfaces

Dynamic extensibility and other forms of dynamic reconfiguration are facilitated by this feature. Each segment of the generic architecture for the DTE systems software interacts with other segments of the local cluster and with peers in remote clusters through carefully defined interfaces. These interfaces are specified in CIFOs (Catalogues of Interface Features and Options). The interfaces are tailorable in that the given set of applications and system requirements for a given cluster determine which features and options will be selected as CIFO subsets for each cluster. The interfaces are extensible in that precisely modeled rules exist for extending these CIFOs as needed over time. As an example of such rules, no device driver can be replaced until certain preconditions are satisfied such as: "Complete all input/output

operations in progress when the replacement command arrives until a 'recoverable' state is reached. Then effect the replacement."

#### F4. Life Cycle Unique Identification

This feature also supports tractable and rigorous reasoning about the MISSION models. In the DTE, classes templates, executable images of objects and messages are uniquely identifiable. For example, suppose an object is a part of an application that requires about five minutes to complete and that is intended to run every hour on the hour. The executable image retains its unique identification but, in addition, each hourly activation receives a different thread-ofcontrol identifier. Each thread assignment is provided a unique identification so that the effects of each activation are traceable. Similarly, an iterative object structure may complete and send the same message structure many times during the life span of each object. In the MISSION approach, the effects of each message are intended to be traceable through the unique identifiers of each message, source, and destination(s). The element of the MISSION approach has been strongly influenced by the work of Moss [24].

## F5. Extensible and Modifiable RunTime Sets

This feature complements all the preceding features, but is particularly germane to: "F3. Tailorable and Extensible Interfaces". The ability to tailor and extend CIFOs in the host and integration environment is important, but a corresponding capability is needed for objects inside any cluster partition of an operational, non-stop DTE. More specifically, the interfaces to each segment of a cluster architecture should allow existing class definitions internal to the segment to be modified or new ones to be added. Once the modified or new class definitions are installed, the interfaces should encapsulate the ability to create new objects and messages of the new and modified classes. In addition, the interfaces should support the retirement and replacement of old classes, objects, and messages as needed. This mechanism is analogous to the polymorphism/dynamic binding mechanisms of object-oriented languages

## F6. Separation of Policies and Mechanisms

This feature not only facilitates tractable, rigorous reasoning, but it also facilitates the domain and application engineering processes through separation of concerns. The MISSION approach partitions and allocates policies to various members of the firewalled subsystems. The shared mechanisms used to effect these policies are in the kernel. For example, the DPS is intended to contain polices for the management of shared services and resources within and among clusters. These policies are encapsulated within DPS modeling objects. The effects are somewhat analogous to earlier techniques of operating systems enforcing "table driven" policies. The interpretation and enforcement of the policies encapsulated by the firewalled subsystems is dependent upon the utilization of the kernel mechanisms. This feature is also supported in Alpha.

#### F7. Multilevel Security and Integrity

All threads-of-control are created, assigned, sustained and retired via the MASC kernel. A requirement for each active object (i.e., one with its own thread-of-control) is to maintain a registration of its unique identity and its current capabilities. This is particularly important when the active object is about to request a service of another object. A unique identity is required for the destination object and its services and resources. In addition, two other points should be noted. First, the match of a sender's capabilities to a receiver's list of required access rights should be enforced for each access. Second, these rights may sometimes have to be temporarily sacrificed in the cause of higher level policy issues related to a system's fault tolerance and survivability.

## F8. Synchronous and Asynchronous Communications Mechanisms

The domain of interest to MISSION researchers includes applications requiring telemetry data to be broadcast as it becomes available and without regard for the status of intended receivers at the time of the broadcast. The domain also includes applications such as multidimensional collision avoidance and proximity operations that require hard constrained, real time synchronization

C.W. McKay et al.

and control. The literature on communication mechanisms to support distributed and concurrent processing requirements reveals two distinct solutions with certain advantages claimed for each [22].

The first type of mechanism supports the use of asynchronous transmissions and receptions without blocking the sending process or the receiving process(es). Instead, transmission is a case of "send when ready and then proceed". Reception is a case of "receive when ready, if message is available, and then proceed". Variations of this type of mechanism have also been studied.

The second type of mechanism is used for two distinct cases of synchronous communication. The first case involves an active object which calls for a service from a passive object (a passive object borrows its thread-of-control). This case is analogous to a local thread-of-control in a "main" procedure calling a remote subroutine. That is, the thread and its request are passed to the environment of the called subroutine. After "borrowing" the thread-of- control to execute, the passive object returns both the results and the thread- of-control to the calling environment.

The second case of synchronous communications involves a need for synchronization and exchange of information among two-or-more cooperating, active objects. This case addresses, among other things, the issues of the Ada rendezvous among two cooperating threads-of-control. This support for multiple forms of communications is very different than the approaches taken in many other related projects such as Mars which only use datagrams.

## F9. Adaptable Runtime Services and Resources

The provision of shared system services and resources to an evolving collection of applications is intended to be based upon well-defined policies, configurations and circumstances. Some resources and services will be replicated to maximize availability and fault tolerance. Such redundancy will need to be managed at a variety of levels. At one extreme, the redundant copies could be managed as "hot standbys" which are ready to be substituted for the primary copy at any time. At another extreme, the redundant copy can be substituted for the primary copy only after processing is performed to prepare the "cold standby" to take over. Depending upon criticality, workload, and the status of system resources, the type and amount of redundancy is intended to vary according to adaptable policies.

Another important aspect of adaptable policies is scheduling. Some real-time applications map naturally to a collection of periodic processes. Others are interrupt driven and are aperiodic. Still others have sporadic service requirements that may be of varying frequency and duration. An important aspect of the approach, therefore, is the use of adaptable scheduling policies to maximize support for MASC functions and components under conditions that vary from normal to various types of emergencies. A similar feature is also found in Real Time Mach.

## F10. Stable Storage

Fault tolerance among clusters of distributed MASC systems benefits from the next feature, distributed nested transactions. However, implementation approaches to such transactions require stable storage. Stable storage has two characteristics that facilitate check pointing and recovery. First, it survives temporary losses of power. Second, it is always updated in an atomic operation.

#### F11. Distributed, Nested Transactions

Fault tolerance among interactive, distributed processing clusters is facilitated by support for distributed, nested transactions [24, 26]. This is particularly true when a fault, failure or error can not be detected in a single state vector, but depends instead upon detection of incorrect sequences of processing. Transactions bracket a named collection of operations between "Begin transaction X" and "End transaction X". The effects of the transaction are to make the set of enclosed operations appear to be a single atomic action. That is, either all of the operations complete successfully or the system can detect and recover from the effects of partial completion. Distributed transactions support hierarchies of parallel and distributed operations. Nesting allows higher level transactions to be composed of sets of enclosed transactions. Transactions of this kind can be used to provide fault tolerance and survivability

in the DTE, and also facilitate reasoning in the host and integration environments. Other related projects employing this mechanism include Alpha and Mars.

# F12. System Level Fault Tolerance and Survivability

The MISSION approach leverages systems software to support true systems level fault tolerance and survivability. Since object classes and relationship sets are used to model software, hardware and communications, human interfaces, and interactions with the environment, systems software monitors can be used to monitor and control systems level resources as appropriate.

An important component of the MISSION approach is the concept of coroutines which associate monitors in the DPS with functional objects elsewhere in the system. The job of the monitors is to detect faults, errors, and failures as soon as possible and to then provide support for effecting isolation, analysis, and recovery. Such detection is based upon assertions that are associated with MASC properties. These assertions may be about values of state or about sequences of state transformations. The Mars project also employs kernel-level mechanisms to support system-level fault tolerance.

#### 3.5 Firewalled partitions

As mentioned above, and illustrated in Figure 2; the generic architecture employs five firewalled partitions that interact by means of the message passing services provided by the kernel. In this subsection we outline further the role of each subsytem.

#### **Distributed Applications System**

The DAS is the firewalled subsystem containing MASC applications that are to be executed on the MASC computing system. The focus of the research in the DTE is on the generic architecture of the systems software rather than the DAS. The DAS developers are intended to leverage the features and options of this generic architecture to improve runtime support of MASC functions and components.

Only two aspects of the DAS are within the scope of this research project. The first is the set of interfaces to the local cluster and to DAS peers in remote clusters. The second is the set of abstractions made available to applications programming teams to improve safety and affordability. However, another important point should also be understood about a DAS partition of a cluster. Any component within a DAS application is firewalled from the other partitions and from other applications within the DAS. That is, different applications and partitions have no direct means of communication, but must invoke a message service of the kernel. This additional firewalling of applications is also supported within the other partitions and is used to facilitate tractable, rigorous reasoning about the individual parts of a partition.

#### **Distributed Information System**

The DIS is responsible for managing shared and persistent information services and resour-Whenever information is shared by more ces. than one application, access to the information is provided via a virtual interface set by requesting services from the DIS. For example, a DAS component could request a unit of shared information from the DIS by invoking a message service from the kernel. Also, some applications do not execute continuously and have requirements for persistent information. For example, a program that takes five minutes to complete may be scheduled to execute once every eight hours. At each execution, the program updates some information in the DIS that must persist between executions. In addition, the DIS manages shared and persistent information on behalf of the systems software. Examples include: performance and workload by cluster, LAN, WAN, and system; health and status of ..., etc. As with the other firewalled partitions, portions of multiple DISs may reside on the same cluster. Each DIS represented on the cluster is firewalled from the other DISs also on the cluster.

The class of MASC computing applications and systems addressed by MISSION will typically be long lived. Many type definitions that will be needed in the future cannot be known when the system is initially developed and deployed. Since non-stop operation requirements prohibit brin-

C.W. McKay et al.

ging the system down to recompile existing code in the context of the new type definitions, an alternative is needed to upgrade the system. The approach under study is based upon controlled inheritance. A set of commands in the Distributed Command Interpreter is intended to allow the MICE to first extend/add the definitions and then create instances of the types. The reader should note that the problem of dynamic type extensibility is not limited to just the DIS.

#### **Distributed Communications System**

The DCS corresponds to the upper three layers and a portion of the fourth layer of the seven laver ISO model for Open Systems Interconnection [33]. (The lower layers are encapsulated as device drivers within the kernel.) The DCS is responsible for managing communications services and resources among clusters, LANs and WANs. Within a cluster, whenever an applications component or a systems software component needs to communicate with a peer at another cluster, the DCS is responsible for effecting this communication. A virtual interface set shared with its DCS peers at other clusters is used to resolve issues of routing, congestion control, relocation, and other services. Such resolution is transparent to the applications components or to any systems software components located outside the DCS partition.

#### **Distributed Policy System**

The DPS is responsible for the evolution and enforcement of policies regarding the sharable services and resources of the integrated systems software. The DPS contains a library of policies which are used in conjunction with the mechanisms of the kernel to manage such issues as: contention between local cluster priorities and universal system priorities, multiparameter scheduling, emergency load shedding, dynamic reconfiguration and others. An important premise is that support can be predictably and dependably provided for different policies needed by different applications if a known set of sufficient resources are available and if a known set of universal and local policies permit. This is somewhat similar to the approaches taken in Alpha and Spring.

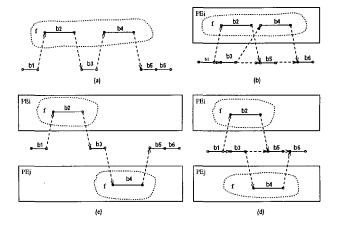

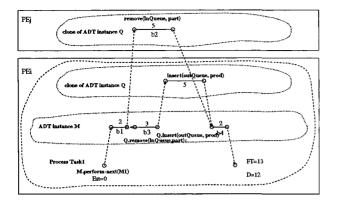

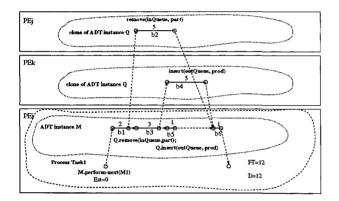

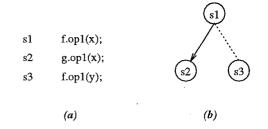

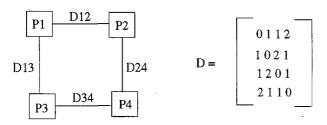

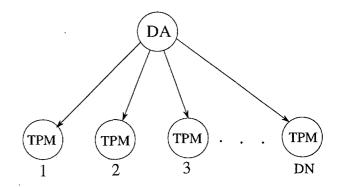

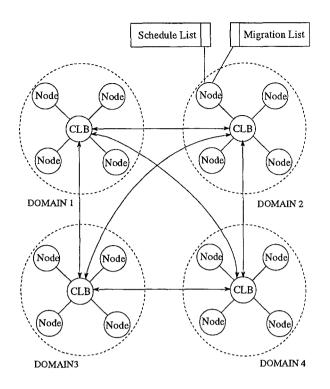

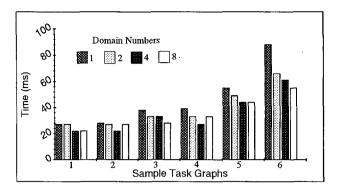

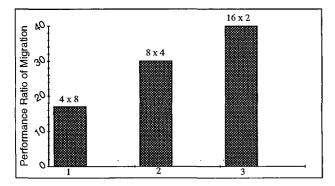

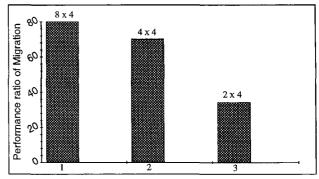

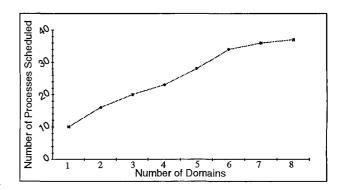

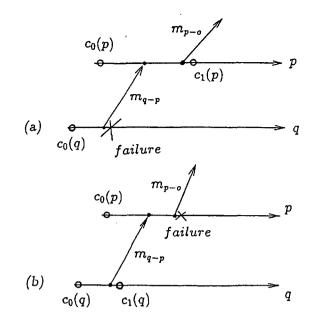

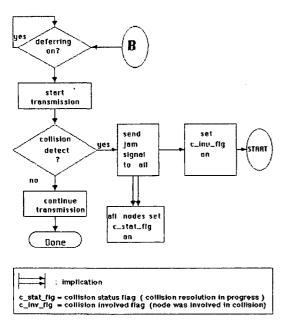

#### **Distributed Monitoring System**